隨著數(shù)字集成電路設(shè)計(jì)在現(xiàn)代電子行業(yè)中的重要性日益提升,Verilog HDL作為一種硬件描述語(yǔ)言,成為工程師和學(xué)生的必備技能。《Verilog HDL數(shù)字集成電路設(shè)計(jì)原理與應(yīng)用(第二版)》是一本深入淺出的教材,全面覆蓋Verilog HDL的基礎(chǔ)知識(shí)、設(shè)計(jì)方法和實(shí)際應(yīng)用。本文將介紹該書的PDF電子書免費(fèi)下載信息,并探討如何結(jié)合軟件開發(fā)工具進(jìn)行高效學(xué)習(xí)。

關(guān)于《Verilog HDL數(shù)字集成電路設(shè)計(jì)原理與應(yīng)用(第二版)》PDF電子書的下載,用戶可以通過多種渠道獲取。正版電子書通常由出版社或授權(quán)平臺(tái)提供,例如,一些教育網(wǎng)站或開源社區(qū)可能提供免費(fèi)樣本或完整版下載。但請(qǐng)注意,下載時(shí)應(yīng)遵守版權(quán)法規(guī),優(yōu)先選擇合法的來源,如官方網(wǎng)站或圖書館資源。這不僅能確保內(nèi)容的準(zhǔn)確性,還能支持作者和出版商的努力。建議搜索關(guān)鍵詞如“Verilog HDL第二版PDF免費(fèi)下載”或訪問相關(guān)學(xué)術(shù)論壇,但務(wù)必核實(shí)來源的可靠性,避免潛在的安全風(fēng)險(xiǎn)。

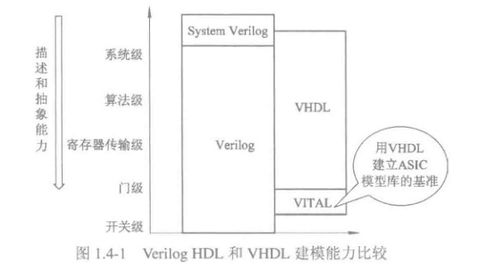

該書的內(nèi)容涵蓋了Verilog HDL的核心原理,包括模塊化設(shè)計(jì)、時(shí)序邏輯、組合邏輯以及高級(jí)主題如測(cè)試臺(tái)和FPGA實(shí)現(xiàn)。對(duì)于初學(xué)者,它提供了循序漸進(jìn)的示例;對(duì)于有經(jīng)驗(yàn)者,則深入講解了實(shí)際工程中的優(yōu)化技巧。通過閱讀此書,讀者可以掌握數(shù)字電路從概念到實(shí)現(xiàn)的全過程。

在軟件開發(fā)方面,結(jié)合Verilog HDL設(shè)計(jì)數(shù)字集成電路時(shí),需要借助專業(yè)的軟件工具。常用的工具包括:

- 仿真工具:如ModelSim或VCS,用于驗(yàn)證設(shè)計(jì)的正確性,通過模擬電路行為來檢測(cè)潛在錯(cuò)誤。

- 綜合工具:如Synopsys Design Compiler,將Verilog代碼轉(zhuǎn)換為門級(jí)網(wǎng)表,為后續(xù)物理實(shí)現(xiàn)奠定基礎(chǔ)。

- FPGA開發(fā)軟件:例如Xilinx Vivado或Intel Quartus,幫助實(shí)現(xiàn)設(shè)計(jì)到可編程邏輯器件的部署。

這些工具通常提供免費(fèi)版本或?qū)W生許可證,用戶可從官方網(wǎng)站下載并安裝。例如,Vivado WebPACK是Xilinx提供的免費(fèi)版本,適合學(xué)習(xí)和原型開發(fā)。

為了高效學(xué)習(xí),建議讀者在下載電子書后,邊閱讀邊實(shí)踐。先從簡(jiǎn)單的Verilog代碼示例開始,使用仿真工具運(yùn)行測(cè)試,逐步構(gòu)建復(fù)雜項(xiàng)目。同時(shí),參與在線社區(qū)如GitHub或Stack Overflow,可以獲取代碼分享和問題解答。

《Verilog HDL數(shù)字集成電路設(shè)計(jì)原理與應(yīng)用(第二版)》是學(xué)習(xí)數(shù)字設(shè)計(jì)的寶貴資源,結(jié)合軟件開發(fā)工具,能夠顯著提升技能水平。希望本文能幫助您順利獲取資料并開始實(shí)踐之旅。記住,持續(xù)學(xué)習(xí)和動(dòng)手實(shí)驗(yàn)是關(guān)鍵!